# OVERALL ROADMAP TECHNOLOGY CHARACTERISTICS

## BACKGROUND

The Overall Roadmap Technology Characteristics (ORTC) tables are created early in the Roadmap process and are used as the basis for initiating the activities of the International Technology Working Groups (ITWGs) in producing their detailed chapters. These tables are also used throughout the renewal effort of the Roadmap as a means of providing synchronization among the TWGs by highlighting inconsistencies between the specific tables. The process to revise the tables includes increasing levels of cross-TWG and international coordination and consensus building to develop underlying models of trends and to reach agreement on target metrics. As a result, the ORTC tables undergo several iterations and reviews.

The metric values of the ORTC tables can be found throughout the Roadmap in greater detail in each Technology Working Group chapter. The information in this section is intended to highlight the current rapid pace of advancement in semiconductor technology. It represents a completion of the revision update and renewal work that began in 2002. Additionally, an ORTC Glossary is provided as an appendix.

## **OVERVIEW OF 2003 REVISIONS**

## DEFINITIONS

As noted above, the Overall Roadmap Technology Characteristics tables provide a consolidated summary of the key technology metrics. Please note that the year header on the tables may refer to different points in the development/life cycle of integrated circuits, depending on the individual line item metric. However, unless otherwise specified for a particular line item, the default year header still refers (as in previous Roadmaps) to the year when product shipment first exceeds 10,000 units per month of ICs from a manufacturing site using "production tooling," Furthermore, a second company must begin production within three months. To satisfy this definition, ASIC production may represent the cumulative volume of many individual product line items processed through the facility.

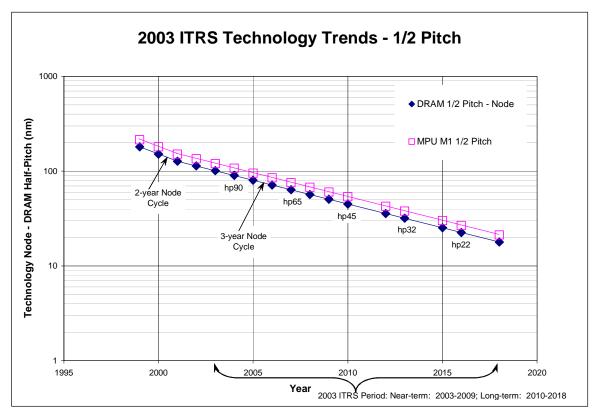

Due to confusion in public press announcements, especially regarding Logic technology "nodes," additional clarification was provided this year by the *ITRS* executive International Roadmap Committee (IRC), adding a technology node designator, "hpXX" to the table header. This designator represents the most aggressive interconnect half-pitch in the industry, which at present is the DRAM cell metal half-pitch. At some point in the future it may be represented by a half-pitch of a different product. Please see the Glossary section for additional details on "Technology Node" and "Production" timing definitions.

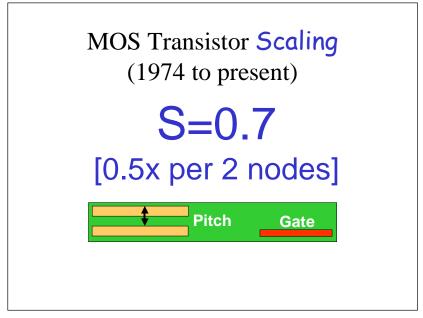

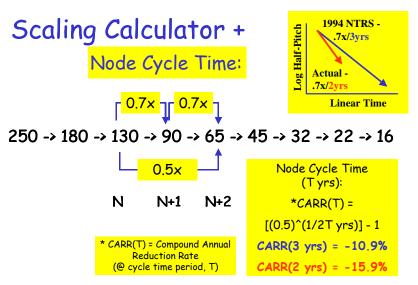

Per previously established IRC guidelines, the 2003 ITRS retains the definition of a technology node as the achievement of significant advancement in the process technology. To be explicit, a technology node is defined as the achievement of an approximate  $0.7 \times$  reduction per node ( $0.5 \times$  per two nodes). Refer to Figure 5. The period of time in which a new technology node is reached is called a "technology-node cycle." Refer to Figure 6. It is acknowledged that continuous improvement occurs between the technology nodes, and this is reflected by including data between nodes in the annual columns of the "Near-term years" tables. The "Long-term years" table columns are three-year increments of the 2003 ITRS timeframe from 2009 (2012, 2015, 2018) and still include the previous ITRS 2001 columns (2010, 2013, 2016) as a reference.

Figure 5 MOS Transistor Scaling—1974 to present

Figure 6 Scaling Calculator

## ROADMAP TIMELINE

The 2003 edition of the Roadmap maintains a 15-year projection, from 2003 as a reference year and through 2018. The timing trend of future technology nodes (three years between nodes) has remained unchanged from the 2001 edition. Therefore, by international consensus, the 90 nm DRAM half-pitch node could begin production ramp between 1Q04 to 4Q04, depending on the completion of customer product qualification, which was made an explicit requirement of the "Production" definition for the 2003 *ITRS*.

In the 2001 ITRS, the 130 nm node was pulled in an additional year (from 2002 in the 1999 ITRS to 2001), anticipating a continuation of an observed historical two-year technology-node cycle calculated from 350 nm/1995, 250 nm node in 1997, 180 nm node in 1999). Data provided by DRAM manufacturers in 2003, which was based upon the rigorous customer-product-qualified production ramp, indicated that the actual production ramp timing was as follows: 350 nm/1995, 250 nm/1998, 180 nm/2000 and 130 nm/2002. This new data indicates a two-year node cycle timing, but delayed one year from the original 2001 ITRS timing. Data gathered on actual DRAM product ramped in 2003 will confirm if the interim node step is 100 nm, per the 2001 and 2003 ITRS, or 110 nm, which would indicate a two-year cycle step between 130 nm/2002 and 90 nm/2004. Although there is the possibility of a continuation of this new delayed two-year-node cycle trend, the present consensus projects a three-year cycle for DRAM interconnect half-pitch nodes throughout the 2003–2018 Roadmap period, as illustrated in Figure 7.

As mentioned above, the DRAM interconnect half-pitch will continue to be used as the most representative feature of leading-edge semiconductor manufacturing technology for defining the achievement of a technology node. However, future data analysis might indicate an aggressive trend for the lagging MPU, ASIC, and Flash metal and/or polysilicon interconnect half-pitches to pass the DRAM half-pitch after 2004, and become the ITRS header node standard. See Figure 7.

## ROUNDED TREND NUMBERS

As a result of the new DRAM half-pitch data inputs, and using the 180 nm node as the calculation standard for trends, the 2003 *ITRS* now includes a correction of the past "rounding" convention for the technology node labels. The actual mathematical trend reduces the nodes by 50% every other node, resulting in an actual versus rounded node number targets, starting from 350 nm in 1995 as follows in Table C.

| YEAR OF<br>Production                   | 1995 | 1998 | 2000 | 2002  | 2003 | 2004 | 2006 | 2007 | 2009 | 2010 | 2012 | 2013 | 2015 | 2016 | 2018 |

|-----------------------------------------|------|------|------|-------|------|------|------|------|------|------|------|------|------|------|------|

|                                         |      |      |      |       |      | hp90 |      | hp65 |      | hp45 |      | hp32 |      | hp22 |      |

| Calculated<br>Trend<br>Numbers (nm)     | 360  | 255  | 180  | 127.3 | 101  | 90   | 71.4 | 63.6 | 50.5 | 45   | 35.7 | 31.8 | 25.3 | 22.5 | 17.9 |

| ITRS<br>Rounded<br>Node<br>Numbers (nm) | 350  | 250  | 180  | 130   | 100  | 90   | 70   | 65   | 50   | 45   | 35   | 32   | 25   | 22   | 18   |

Table C Rounded versus Actual Trend Numbers

Note the new rounding corrections become more critical as the industry moves into the double-digit technology nodes of the new nanotechnology (sub-100 nm) era. Please note also that some regions, for their own past publication consistency, will retain their right to continue to track the previous technology nodes beginning with 100 nm/2003. Starting from 100 nm in 2003 will result in node milestones that are targeted one year earlier than the present 2003 roadmap hpXX convention (70 nm/2006; 50 nm/2009; 35 nm/2012; 25 nm/2015). By consensus of the IRC both node number sets are available for long-term calculations, since the original *2001 ITRS* long-term columns were retained (2010/hp45/45 nm; 2013/hp32/32 nm; 2016/hp22/22 nm), and new columns (2012/35 nm; 2015/25 nm; 2018/18 nm) were added.

## UPDATES TO THE ORTC

A new addition to the 2003 ITRS ORTC technology target line items is the Logic Metal 1 (M1) half-pitch. This was added to the ORTC Table 1a and 1b in addition to the unchanged polysilicon half-pitch in order to be consistent with observed industry status and also to be consistent with the Interconnect TWG logic pitch targets, which track contacted Metal 1 rather than the 2001 ITRS un-contacted polysilicon half-pitch.

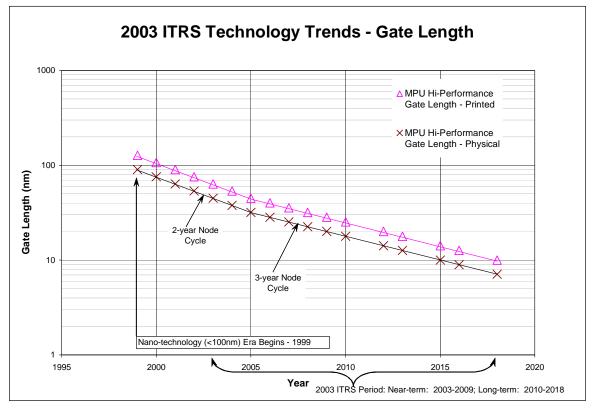

The *printed* MPU gate length received a major correction to more an aggressive starting point in the 2001 ITRS. In addition, a new *physical* gate length is being tracked that further reduces the bottom gate length dimension of a fully processed transistor. Both the printed and physical gate length trends remain unchanged for the 2003 ITRS, and are forecast to continue scaling by about 70% per two-year cycle through the 32 nm physical MPU gate length in 2005, but are expected to return to a three-year cycle trend thereafter, consistent with the present DRAM half-pitch trend forecast. Refer to Figure 8.

The ORTC metrics are often used by semiconductor companies as a set of targets that need to be achieved ahead of schedule to secure industry leadership. Thus, the highly competitive environment of the semiconductor industry quickly tends to make obsolete many portions of the ORTC metrics and, consequently, the Roadmap. Hopefully, the gathering and analysis of actual data, combined with the ITRS annual update process will provide sufficiently close tracking of the evolving international consensus on technology directions to maintain the usefulness of the *ITRS* to the industry.

For example, the actual data and conference papers, along with company survey data and public announcements will be re-evaluated during the year 2004 *ITRS* update process, and the possibility of a continued two-year node cycle. In addition, logic and Flash product half-pitch acceleration will be monitored for future header leadership candidates.

As mentioned above, to reflect the variety of cycles and to allow for closer monitoring of future roadmap shifts, it was agreed to continue the practice of publishing annual technology requirements from 2003 through 2009, called the "Near-term Years," and at three-year (node) intervals thereafter, called the "Long-term years" (2012, 2015, 2018), while retaining the previous *2001 ITRS* long-term columns for ease of comparison and to retain the tracking of the three-year cycle nodes.

Figure 7 2003 ITRS—Half Pitch Trends

Figure 8 2003 ITRS—Gate Length Trends

## PRODUCT GENERATIONS AND CHIP-SIZE MODEL

This section discusses "product generations" and their relationship to the technology nodes, since, in the past, these terms have often been used interchangeably. However, the historically simple picture of a new DRAM product generation every three years (at  $4 \times$  the previous density and based on an essentially new set of technology features) has become obsolete as a way to define technology nodes. For this 2003 ITRS edition, the "technology node" is still linked to an anticipated DRAM feature size (minimum metal or polysilicon half-pitch). However, implications of this connection are diminishing as the product evolution/shrink path becomes more complex.

Historically, DRAM products have been recognized as the technology drivers for the entire semiconductor industry. Prior to the early 1990s, logic (as exemplified by MPU) technology was developed at a slower pace than DRAM technology. During the last few years, the development rate of new technologies used to manufacture microprocessors has accelerated. Microprocessor products are closing the half-pitch technology gap with DRAM, and are now driving the most leading-edge lithography tools and processes—especially for the capability to process the isolated-line feature of the printed and physical gate length. With this 2003 Roadmap it is recognized that DRAM and microprocessor products share the technology leadership role.

However, several fundamental differences exist between the two families of products. Due to strong commodity market economic pressure to reduce cost and increase fab output productivity, DRAM product emphasizes the minimization of the chip size. Therefore development of DRAM technology focuses mainly on minimization of the area occupied by the memory cell. However, this pressure to minimize cell size is in conflict with the requirement to maximize the capacitance of the cell for charge storage performance, which puts pressure on memory cell designers to find creative ways through design and materials to meet minimum capacitance requirements while reducing cell size. In addition, to closely pack the highest number of DRAM cells in the smallest area requires minimization of cell pitch.

Microprocessors have also come under strong market pressure to reduce costs while maximizing performance. Performance is enabled primarily by the length of the transistor gate and by the number of interconnect layers. The 2003 *ITRS* teams have reached consensus on models for the required functionality, chip size, cell area, and density for the

ORTC tables. Additional line items were added to communicate the model consensus, and the underlying model assumptions are included in the ORTC table notations. Table 1a and 1b summarize the near and long-term technology node metrics. As agreed, the key *ITRS* technology node identifier would continue to be the DRAM half-pitch, but also included are the aggressive MPU gate-length performance-driven feature sizes. For completeness, the MPU/ASIC product metal half-pitch are also tracked and that will trail slightly behind or equal to the DRAM half-pitch. The ASIC/low power gate lengths are also included, and lag behind the leading-edge MPU in order to maximize standby and operating current drain. See the Glossary section for additional detail on the definition of the half-pitch and gate-length features. For each product generation, both the leading-edge ("at introduction") and the high-volume ("at production") DRAM products are included.

It should be noted that the long-term average annualized reduction rate in feature size is projected to continue at approximately 11%/year (~30% reduction/three years), even though this rate accelerated to approximately 16%/year (~30% reduction/two years) in the time interval 1995–2001 (refer to Figure 5). As mentioned above, the overall schedule for introduction of a new product generation has been accelerated by one additional year.

|                                                      | -    |      |      | 0.   |      |      |      |

|------------------------------------------------------|------|------|------|------|------|------|------|

| Year of Production                                   | 2003 | 2004 | 2005 | 2006 | 2007 | 2008 | 2009 |

| Technology Node                                      |      | hp90 |      |      | hp65 |      |      |

| DRAM ½ Pitch (nm)                                    | 100  | 90   | 80   | 70   | 65   | 57   | 50   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                   | 120  | 107  | 95   | 85   | 76   | 67   | 60   |

| MPU/ASIC 1/2 Pitch (nm) (Un-contacted Poly)          | 107  | 90   | 80   | 70   | 65   | 57   | 50   |

| MPU Printed Gate Length (nm) ††                      | 65   | 53   | 45   | 40   | 35   | 32   | 28   |

| MPU Physical Gate Length (nm)                        | 45   | 37   | 32   | 28   | 25   | 22   | 20   |

| ASIC/Low Operating Power Printed Gate Length (nm) †† | 90   | 75   | 65   | 53   | 45   | 40   | 35   |

| ASIC/Low Operating Power Physical Gate Length (nm)   | 65   | 53   | 45   | 37   | 32   | 28   | 25   |

Table 1a Product Generations and Chip Size Model Technology Nodes—Near-term Years

| Table 1b | Product Generations | s and Chip Size Model | Technology Nodes—Long-term Years |

|----------|---------------------|-----------------------|----------------------------------|

|----------|---------------------|-----------------------|----------------------------------|

| Year of Production                                   | 2010 | 2012 | 2013 | 2015 | 2016 | 2018 |

|------------------------------------------------------|------|------|------|------|------|------|

| Technology Node                                      | hp45 |      | hp32 |      | hp22 |      |

| DRAM ½ Pitch (nm)                                    | 45   | 35   | 32   | 25   | 22   | 18   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                   | 54   | 42   | 38   | 30   | 27   | 21   |

| MPU/ASIC 1/2 Pitch (nm) (Un-contacted Poly)          | 45   | 35   | 32   | 25   | 22   | 18   |

| MPU Printed Gate Length (nm) ††                      | 25   | 20   | 18   | 14   | 13   | 10   |

| MPU Physical Gate Length (nm)                        | 18   | 14   | 13   | 10   | 9    | 7    |

| ASIC/Low Operating Power Printed Gate Length (nm) †† | 32   | 25   | 22   | 18   | 16   | 13   |

| ASIC/Low Operating Power Physical Gate Length (nm)   | 22   | 18   | 16   | 13   | 11   | 9    |

#### Notes for Tables 1a and 1b:

*††* MPU and ASIC gate-length (in resist) node targets refer to the most aggressive requirements, as printed in photoresist (which was by definition also "as etched in polysilicon," in the 1999 ITRS).

However, during the 2000/2001 ITRS development, trends were identified, in which the MPU and ASIC "physical" gate lengths may be reduced from the "as-printed" dimension. These "physical" gate-length targets are driven by the need for maximum speed performance in logic Microprocessor (MPU) products, and are included in the Front End Processes (FEP), Process Integration, Devices, and Structures (PIDs), and Design ITWG Tables as needs that drive device design and process technology requirements.

In addition, during the 2003 ITRS development, an attempt has been made to reconcile the many published press releases by Logic manufacturers referencing "90 nm" technology node manufacturing in 2003. Since the metal 1 (M1) half-pitch of actual devices was cited at 110–120 nm, confusion arose regarding the relationship to the ITRS DRAM half-pitch-based header targets. After conversation with leading-edge manufacturers, it was determined that the public citations were in reference to an "indexed" technology node roadmap that represented the average of the half-pitch (for density) and the printed gate length (for speed performance).

The IRC has decided that the best way to minimize confusion between the ITRS and individual company public announcements is to identify the ITRS table header node with the industry's most aggressive half-pitch targets, and to label these targets as hpXX (i.e., hp90, hp65, hp45, etc.). Currently the industry's most aggressive half pitch is the DRAM cell metal half-pitch.

| Year of Production                               | 2003   | 2004   | 2005   | 2006   | 2007   | 2008   | 2009   |

|--------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|

| Technology Node                                  |        | hp90   |        |        | hp65   |        |        |

| DRAM ½ Pitch (nm)                                | 100    | 90     | 80     | 70     | 65     | 57     | 50     |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)               | 120    | 107    | 95     | 85     | 76     | 67     | 60     |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)        | 107    | 90     | 80     | 70     | 65     | 57     | 50     |

| MPU Printed Gate Length (nm) ††                  | 65     | 53     | 45     | 40     | 35     | 32     | 28     |

| MPU Physical Gate Length (nm)                    | 45     | 37     | 32     | 28     | 25     | 22     | 20     |

| Cell area factor [a]                             | 8      | 8      | 7.5    | 7      | 7      | 6      | 6      |

| Cell area $[Ca = af^2] (mm^2)$                   | 0.082  | 0.065  | 0.048  | 0.036  | 0.028  | 0.019  | 0.015  |

| Cell array area at production (% of chip size) § | 63.00% | 63.00% | 63.00% | 63.00% | 63.00% | 63.00% | 63.00% |

| Generation at production §                       | 1G     | 1G     | 1G     | 2G     | 2G     | 4G     | 4G     |

| Functions per chip (Gbits)                       | 1.07   | 1.07   | 1.07   | 2.15   | 2.15   | 4.29   | 4.29   |

| Chip size at production (mm <sup>2</sup> )§      | 139    | 110    | 82     | 122    | 97     | 131    | 104    |

| <i>Gbits/cm<sup>2</sup> at production §</i>      | 0.77   | 0.97   | 1.31   | 1.76   | 2.22   | 3.27   | 4.12   |

Table 1c DRAM Production Product Generations and Chip Size Model—Near-term Years

Table 1d

DRAM Production Product Generations and Chip Size Model—Long-term Years

| Year of Production                               | 2010   | 2012   | 2013   | 2015   | 2016   | 2018   |

|--------------------------------------------------|--------|--------|--------|--------|--------|--------|

| Technology Node                                  | hp45   |        | hp32   |        | hp22   |        |

| DRAM 1/2 Pitch (nm)                              | 45     | 35     | 32     | 25     | 22     | 18     |

| MPU/ASIC Metal 1 (M1) 1/2 Pitch (nm)             | 54     | 42     | 38     | 30     | 27     | 21     |

| MPU/ASIC 1/2 Pitch (nm) (Un-contacted Poly)      | 45     | 35     | 32     | 25     | 22     | 18     |

| MPU Printed Gate Length (nm) ††                  | 25     | 20     | 18     | 14     | 13     | 10     |

| MPU Physical Gate Length (nm)                    | 18     | 14     | 13     | 10     | 9      | 7      |

| Cell area factor [a]                             | 6      | 6      | 6      | 6      | 5      | 5      |

| Cell area $[Ca = af^2] (mm^2)$                   | 0.012  | 0.0077 | 0.0061 | 0.0038 | 0.0025 | 0.0016 |

| Cell array area at production (% of chip size) § | 63.00% | 63.0%  | 63.0%  | 63.0%  | 63.0%  | 63.0%  |

| Generation at production §                       | 4G     | 8G     | 8G     | 16g    | 32G    | 32G    |

| Functions per chip (Gbits)                       | 4.29   | 8.59   | 8.59   | 17.18  | 34.36  | 34.36  |

| Chip size at production (mm <sup>2</sup> )§      | 83     | 104    | 83     | 104    | 138    | 87     |

| <i>Gbits/cm<sup>2</sup> at production §</i>      | 5.19   | 8.23   | 10.37  | 16.46  | 24.89  | 39.51  |

Notes for Tables 1c and 1d:

§ DRAM Model—Cell Factor (design/process improvement) targets are as follows:

1999-2004/8x: 2005/7.5x; 2006-2007/7x; 2008-2015/6x; 2016–2018/5x. The delay of the "6" DRAM cell design improvement factor [a] by five years, from 2003 to 2008, requires the slowing of the addition of "Moore's Law" bits/chip from 2× every 1.5–2 years to 2× every 2.5–3 years in the 2003 ITRS DRAM Chip Size Model, which remains on a three-year DRAM half-pitch node cycle after 2004.

DRAM product generations are usually increased by 4×bits/chip every four years with interim 2×bits/chip generations, except:

1. at the Introduction phase, after the 16 Gbit generation, the introduction rate is  $4 \times six$  years ( $2 \times three$  years); and

2. at the Production phase, after the 1 Gbit generation, the introduction rate is  $4 \times five$  years ( $2 \times two-three$  years).

InTER-generation chip size growth rate model target for Production-phase DRAMs is now "flat" at less than 140 mm<sup>2</sup>, similar to the MPU model. This new flat-chip-size model target requires the bits/chip "Moore's Law" model for DRAMs to increase the time for doubling bits per chip to an average of  $2\times2.5$  years by alternating between  $2\times2$  years and  $2\times3$  years (see ORTC Table 1c,d). In addition, the Cell Array Efficiency (Array % of total chip area) was increased to 63%, which also assists in the achievement of the target flat-chip-size model for the Production-phase product chip size, even under the slower design improvement factor contribution (see note above). The InTRA-generation chip size shrink model is  $0.5\times$  every technology node in-between cell factor reductions.

| Year of Production                                 | 2003   | 2004   | 2005   | 2006   | 2007   | 2008   | 2009   |

|----------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|

| Technology Node                                    |        | hp90   |        |        | hp65   |        |        |

| DRAM ½ Pitch (nm)                                  | 100    | 90     | 80     | 70     | 65     | 57     | 50     |

| DRAM ½ Pitch (nm)                                  | 100    | 90     | 80     | 70     | 65     | 57     | 50     |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                 | 120    | 107    | 95     | 85     | 76     | 67     | 60     |

| MPU/ASIC 1/2 Pitch (nm) (Un-contacted Poly)        | 107    | 90     | 80     | 70     | 65     | 57     | 50     |

| MPU Printed Gate Length (nm) ††                    | 65     | 53     | 45     | 40     | 35     | 32     | 28     |

| MPU Physical Gate Length (nm)                      | 45     | 37     | 32     | 28     | 25     | 22     | 20     |

| Cell area factor [a]                               | 8      | 8      | 7.5    | 7      | 7      | 6      | 6      |

| Cell area $[Ca = af^2] (mm^2)$                     | 0.082  | 0.065  | 0.048  | 0.036  | 0.028  | 0.019  | 0.015  |

| Cell array area at introduction (% of chip size) § | 72.23% | 72.61% | 72.95% | 73.25% | 73.52% | 73.76% | 73.97% |

| Generation at introduction §                       | 4G     | 4G     | 8G     | 8G     | 16G    | 16G    | 16G    |

| Functions per chip (Gbits)                         | 4.29   | 4.29   | 8.59   | 8.59   | 17.18  | 17.18  | 17.18  |

| Chip size at introduction $(mm^2)$ §               | 485    | 383    | 568    | 419    | 662    | 449    | 356    |

| Gbits/cm <sup>2</sup> at introduction §            | 0.88   | 1.12   | 1.51   | 2.05   | 2.59   | 3.82   | 4.83   |

Table 1e

DRAM Introduction Product Generations and Chip Size Model—Near-term Years

Table 1f DRAM Introduction Product Generations and Chip Size Model—Long-term Years

| Year of Production                                 | 2010   | 2012   | 2013   | 2015   | 2016   | 2018   |

|----------------------------------------------------|--------|--------|--------|--------|--------|--------|

| Technology Node                                    | hp45   |        | hp32   |        | hp22   |        |

| DRAM ½ Pitch (nm)                                  | 45     | 35     | 32     | 25     | 22     | 18     |

| MPU/ASIC Metal 1 (M1) 1/2 Pitch (nm)               | 54     | 42     | 38     | 30     | 27     | 21     |

| MPU/ASIC 1/2 Pitch (nm) (Un-contacted Poly)        | 45     | 35     | 32     | 25     | 22     | 18     |

| MPU Printed Gate Length (nm) ††                    | 25     | 20     | 18     | 14     | 13     | 10     |

| MPU Physical Gate Length (nm)                      | 18     | 14     | 13     | 10     | 9.0    | 7.0    |

| Cell area factor [a]                               | 6      | 6      | 6      | 6      | 5      | 5      |

| Cell area $[Ca = af2] (mm^2)$                      | 0.012  | 0.0077 | 0.0061 | 0.0038 | 0.0025 | 0.0016 |

| Cell array area at introduction (% of chip size) § | 74.16% | 74.47% | 74.61% | 74.83% | 74.93% | 75.09% |

| Generation at introduction §                       | 32G    | 32G    | 64G    | 64G    | 128G   | 128G   |

| Functions per chip (Gbits)                         | 34.36  | 34.36  | 68.72  | 68.7   | 137.4  | 137.4  |

| Chip size at introduction $(mm^2)$ §               | 563    | 353    | 560    | 351    | 464    | 292    |

| Gbits/cm2 at introduction §                        | 5.2    | 8.2    | 10.4   | 16.5   | 24.9   | 39.5   |

Notes for Tables 1e and 1f:

§ DRAM Model—Cell Factor (design/process improvement) targets are as follows:

1999-2004/8x: 2005/7.5x; 2006-2007/7x; 2008-2015/6x; 2016–2018/5x. The delay of the "6" DRAM Cell design improvement Factor [a] by five years, from 2003 to 2008, requires the slowing of the addition of "Moore's Law" bits/chip from 2× every 1.5–2 years to 2× every 2.5–3 years in the 2003 ITRS DRAM Chip Size Model, which remains on a 3-year DRAM half-pitch node cycle after 2004.

DRAM product generations are usually increased by 4×bits/chip every four years with interim 2×bits/chip generations, except:

1. at the Introduction phase, after the 16 Gbit generation/2007, the introduction rate is 4% six years (2% three years); and

2. at the Production phase, after the 1 Gbit generation/2003, the introduction rate is 4×/five years (2×/two-three years).

The original 2001 ITRS InTER-generation chip size growth rate was targeted to fit one chip per 572 mm<sup>2</sup> field at Introduction and two chips per 572 mm<sup>2</sup> field at Production. Due to the delay of the cell area factor reductions, Introduction chip sizes increased, but the new 704 mm<sup>2</sup> maximum affordable Litho field allows the Introduction chip to double bits per chip every two years through the 16 Gbit generation (660 mm<sup>2</sup>/2007). Slowing the "Moore's Law" bits per chip of the Introduction-phase DRAM model to an average of 2× per 2.5 years enables the Introduction DRAMs to remain under the original 572 mm<sup>2</sup> affordable target after 2007. The InTRA-generation chip size shrink model remains at 0.5× every technology node inbetween cell factor reductions, and eventually (ranging from five to six years), the Introduction-phase DRAMs shrink below the 140 mm<sup>2</sup> Production-phase chip size target.

| Year of Production                                                                             | 2003  | 2004  | 2005  | 2006  | 2007  | 2008  | 2009  |

|------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Technology Node                                                                                |       | hp90  |       |       | hp65  |       |       |

| DRAM ½ Pitch (nm)                                                                              | 100   | 90    | 80    | 70    | 65    | 57    | 50    |

| DRAM ½ Pitch (nm)                                                                              | 100   | 90    | 80    | 70    | 65    | 57    | 50    |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                             | 120   | 107   | 95    | 85    | 76    | 67    | 60    |

| MPU/ASIC 1/2 Pitch (nm) (Un-contacted Poly)                                                    | 107   | 90    | 80    | 70    | 65    | 57    | 50    |

| MPU Printed Gate Length (nm) ††                                                                | 65    | 53    | 45    | 40    | 35    | 32    | 28    |

| MPU Physical Gate Length (nm)                                                                  | 45    | 37    | 32    | 28    | 25    | 22    | 20    |

| SRAM Cell (6-transistor) Area factor ++                                                        | 120.3 | 117.8 | 115.6 | 113.7 | 111.9 | 110.4 | 109.0 |

| Logic Gate (4-transistor) Area factor ++                                                       | 320   | 320   | 320   | 320   | 320   | 320   | 320   |

| SRAM Cell (6-transistor) Area efficiency ++                                                    | 0.63  | 0.63  | 0.63  | 0.63  | 0.63  | 0.63  | 0.63  |

| Logic Gate (4-transistor) Area efficiency ++                                                   | 0.50  | 0.50  | 0.50  | 0.50  | 0.50  | 0.50  | 0.50  |

| SRAM Cell (6-transistor) Area w/overhead ++                                                    | 2.0   | 1.5   | 1.2   | 0.93  | 0.73  | 0.57  | 0.45  |

| Logic Gate (4-transistor) Area w/overhead ++                                                   | 6.5   | 5.2   | 4.1   | 3.3   | 2.6   | 2.1   | 1.6   |

| Transistor density SRAM (Mtransistors/cm <sup>2</sup> )                                        | 305   | 393   | 504   | 646   | 827   | 1,057 | 1,348 |

| Transistor density logic (Mtransistors/cm <sup>2</sup> )                                       | 61    | 77    | 97    | 122   | 154   | 194   | 245   |

| Generation at introduction *                                                                   |       | p07c  |       |       | p10c  |       |       |

| Functions per chip at introduction<br>(million transistors [Mtransistors])                     | 180   | 226   | 285   | 360   | 453   | 571   | 719   |

| Chip size at introduction $(mm^2)$ ‡                                                           | 280   | 280   | 280   | 280   | 280   | 280   | 280   |

| Cost performance MPU (Mtransistors/cm <sup>2</sup> at introduction) (including on-chip SRAM) ‡ | 110   | 138   | 174   | 219   | 276   | 348   | 438   |

| Generation at production *                                                                     |       | p04c  |       |       | p07c  |       |       |

| Functions per chip at production<br>(million transistors [Mtransistors])                       | 153   | 193   | 243   | 307   | 386   | 487   | 614   |

| Chip size at production $(mm^2)$ §§                                                            | 140   | 140   | 140   | 140   | 140   | 140   | 140   |

| Cost performance MPU (Mtransistors/cm <sup>2</sup> at production, including on-chip SRAM) ‡    | 110   | 138   | 174   | 219   | 276   | 348   | 438   |

Table 1gMPU (High-volume Microprocessor) Cost-Performance Product Generations and<br/>Chip Size Model—Near-term Years

| Year of Production                                                                             | 2010  | 2012  | 2013  | 2015  | 2016  | 2018   |

|------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|--------|

| Technology Node                                                                                | hp45  |       | hp32  |       | hp22  |        |

| DRAM ½ Pitch (nm)                                                                              | 45    | 35    | 32    | 25    | 22    | 18     |

| DRAM ½ Pitch (nm)                                                                              | 45    | 35    | 32    | 25    | 22    | 18     |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                             | 54    | 42    | 38    | 30    | 27    | 21     |

| MPU/ASIC 1/2 Pitch (nm) (Un-contacted Poly)                                                    | 45    | 35    | 32    | 25    | 22    | 18     |

| MPU Printed Gate Length (nm) ††                                                                | 25    | 20    | 18    | 14    | 13    | 10     |

| MPU Physical Gate Length (nm)                                                                  | 18    | 14    | 13    | 10    | 9     | 7      |

| SRAM Cell (6-transistor) Area factor ++                                                        | 107.8 | 105.7 | 104.8 | 103.4 | 102.8 | 101.7  |

| Logic Gate (4-transistor) Area factor ++                                                       | 320   | 320   | 320   | 320   | 320   | 320    |

| SRAM Cell (6-transistor) Area efficiency ++                                                    | 0.625 | 0.625 | 0.625 | 0.625 | 0.625 | 0.625  |

| Logic Gate (4-transistor) Area efficiency ++                                                   | 0.500 | 0.500 | 0.500 | 0.500 | 0.500 | 0.500  |

| SRAM Cell (6-transistor) Area w/overhead ++                                                    | 0.22  | 0.13  | 0.11  | 0.066 | 0.052 | 0.032  |

| Logic Gate (4-transistor) Area w/overhead ++                                                   | 1.30  | 0.82  | 0.65  | 0.41  | 0.32  | 0.20   |

| Transistor density SRAM (Mtransistors/cm <sup>2</sup> )                                        | 1,718 | 2,781 | 3,532 | 5,687 | 7,208 | 11,558 |

| Transistor density logic (Mtransistors/cm <sup>2</sup> )                                       | 309   | 490   | 617   | 980   | 1,235 | 1,960  |

| Generation at introduction *                                                                   | p13c  |       | p16c  |       | p19c  |        |

| Functions per chip at introduction (million transistors [Mtransistors])                        | 1,546 | 2,454 | 3,092 | 4,908 | 6,184 | 9,816  |

| Chip size at introduction $(mm^2)$ ‡                                                           | 280   | 280   | 280   | 280   | 280   | 280    |

| Cost performance MPU (Mtransistors/cm <sup>2</sup> at introduction) (including on-chip SRAM) ‡ | 552   | 876   | 1,104 | 1,753 | 2,209 | 3,506  |

| Generation at production *                                                                     | p10c  |       | p13c  |       | p16c  |        |

| Functions per chip at production (million transistors [Mtransistors])                          | 773   | 1,227 | 1,546 | 2,454 | 3,092 | 4,908  |

| Chip size at production (mm <sup>2</sup> ) §§                                                  | 140   | 140   | 140   | 140   | 140   | 140    |

| Cost performance MPU (Mtransistors/cm <sup>2</sup> at production, including on-chip SRAM) ‡    | 552   | 876   | 1,104 | 1,753 | 2,209 | 3,506  |

Table 1hMPU (High-volume Microprocessor) Cost-Performance Product Generations and Chip Size<br/>Model—Long-term Years

Notes for Tables 1g and 1h:

++ The MPU area factors are analogous to the "cell area factor" for DRAMs. The reduction of area factors has been achieved historically through a combination of many factors, for example—use of additional interconnect levels, self-alignment techniques, and more efficient circuit layout. However, recent data has indicated that the improvement (reduction) of the area factors is slowing, and is virtually flat for the logic gate area factor.

\* p is processor, numerals reflect year of production; c indicates cost-performance product. Examples—the cost-performance processor, p01c, was introduced in 1999, but not ramped into volume production until 2001; similarly, the p04c, is introduced in 2001, but is targeted for volume production in 2004.

*‡ MPU Cost-performance Model—Cost-performance MPU includes Level 2 (L2) on-chip SRAM (512Kbyte/1999), and the combination of both SRAM and logic transistor functionality doubles every technology node cycle.*

§§ MPU Chip Size Model—Both the cost-performance and high-performance MPUs InTER-generation chip size growth rates are targeted to be flat through 2018 (280 mm<sup>2</sup>/cost-performance at introduction; 140 mm<sup>2</sup>/cost-performance at production; 310 mm<sup>2</sup>/high-performance at production). The MPU flat chip-size model is made possible by doubling the on-chip functionality every technology node cycle. The InTRA-generation chip size shrink model was 0.5× every two-year technology node through 2001, and is now 0.5× every three-year technology node cycle after 2003.

Refer to the Glossary for definitions

| Year of Production                                                                                            | 2003 | 2004  | 2005  | 2006  | 2007  | 2008  | 2009  |

|---------------------------------------------------------------------------------------------------------------|------|-------|-------|-------|-------|-------|-------|

| Technology Node                                                                                               |      | hp90  |       |       | hp65  |       |       |

| DRAM ½ Pitch (nm)                                                                                             | 100  | 90    | 80    | 70    | 65    | 57    | 50    |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                            | 120  | 107   | 95    | 85    | 76    | 67    | 60    |

| MPU/ASIC 1/2 Pitch (nm) (Un-contacted Poly)                                                                   | 107  | 90    | 80    | 70    | 65    | 57    | 50    |

| MPU Printed Gate Length (nm) ††                                                                               | 65   | 53    | 45    | 40    | 35    | 32    | 28    |

| MPU Physical Gate Length (nm)                                                                                 | 45   | 37    | 32    | 28    | 25    | 22    | 20    |

| Logic (Low-volume Microprocessor) High-performance ‡                                                          |      |       |       |       |       |       |       |

| Generation at production **                                                                                   | p03h |       | p05h  |       | p07h  |       | p09h  |

| Functions per chip (million transistors)                                                                      | 439  | 553   | 697   | 878   | 1,106 | 1,393 | 1,756 |

| Chip size at production (mm <sup>2</sup> ) §§                                                                 | 310  | 310   | 310   | 310   | 310   | 310   | 310   |

| High-performance MPU Mtransistors/cm <sup>2</sup> at production (including on-chip SRAM) ‡                    | 142  | 178   | 225   | 283   | 357   | 449   | 566   |

| ASIC                                                                                                          |      |       |       |       |       |       |       |

| ASIC usable Mtransistors/cm <sup>2</sup> (auto layout)                                                        | 142  | 178   | 225   | 283   | 357   | 449   | 566   |

| ASIC max chip size at production (mm <sup>2</sup> ) (maximum lithographic field size)                         | 572  | 572   | 572   | 572   | 572   | 572   | 572   |

| ASIC maximum functions per chip at production<br>(Mtransistors/chip) (fit in maximum lithographic field size) | 810  | 1,020 | 1,286 | 1,620 | 2,041 | 2,571 | 3,239 |

Table 1i High-Performance MPU and ASIC Product Generations and Chip Size Model—Near-term Years

|                                                                                                         |       |       | -     |        |        |        |

|---------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|--------|--------|

| Year of Production                                                                                      | 2010  | 2012  | 2013  | 2015   | 2016   | 2018   |

| Technology Node                                                                                         | hp45  |       | hp32  |        | hp22   |        |

| DRAM ½ Pitch (nm)                                                                                       | 45    | 35    | 32    | 25     | 22     | 18     |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                      | 54    | 42    | 38    | 30     | 27     | 21     |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)                                                               | 45    | 35    | 32    | 25     | 22     | 18     |

| MPU Printed Gate Length (nm) ††                                                                         | 25    | 20    | 18    | 14     | 13     | 10     |

| MPU Physical Gate Length (nm)                                                                           | 18    | 14    | 13    | 10     | 9      | 7      |

| Logic (Low-volume Microprocessor) High-performance ‡                                                    |       |       |       | •      |        |        |

| Generation at production **                                                                             |       |       | p13h  | p15h   |        |        |

| Functions per chip (million transistors)                                                                | 2,212 | 3,511 | 4,424 | 7,022  | 8,848  | 14,045 |

| Chip size at production (mm <sup>2</sup> ) §§                                                           | 310   | 310   | 310   | 310    | 310    | 310    |

| High-performance MPU Mtransistors/cm <sup>2</sup> at production (including on-chip SRAM) ‡              | 714   | 1,133 | 1,427 | 2,265  | 2,854  | 4,531  |

| ASIC                                                                                                    | •     |       |       | •      |        |        |

| ASIC usable Mtransistors/cm <sup>2</sup> (auto layout)                                                  | 714   | 1,133 | 1,427 | 2,265  | 2,854  | 4,531  |

| ASIC maximum chip size at production (mm <sup>2</sup> )<br>(maximum lithographic field size)            | 572   | 572   | 572   | 572    | 572    | 572    |

| ASIC maximum functions per chip at ramp (Mtransistors/chip)<br>(fit in maximum lithographic field size) | 4,081 | 6,479 | 8,163 | 12,958 | 16,326 | 25,91  |

*Table 1j* High-Performance MPU and ASIC Product Generations and Chip Size Model—Long-term Years

Notes for Tables 1i and 1j:

\*\* p is processor, numerals reflect year of production; h indicates high-performance product. Examples—the high-performance processor, p99h, was ramped into volume production in 1999; similarly, the p01h, is introduced in 2001, the p03h in2003, and so forth.

*‡ MPU* High-performance Model—High-performance MPU includes large L2 and L3 on-chip SRAM (2MByte/1999) plus a larger logic core (P99h core = 25M transistor (Mtransistors) both SRAM and Logic functionality doubles every technology node cycle.

§§ MPU Chip Size Model—Both the cost-performance and high-performance MPUs InTER-generation chip size growth rates are targeted to be flat through 2018 (280 mm<sup>2</sup>/cost-performance at introduction; 140 mm<sup>2</sup>/cost-performance at production; 310 mm<sup>2</sup>/high-performance at production). The MPU flat chip-size model is made possible by doubling the on-chip functionality every technology node cycle. The InTRA-generation chip size shrink model was 0.5× every two-year technology node through 2001, and is now 0.5× every three-year technology node cycle after 2003.

Refer to the Glossary for definitions

## CHIP-SIZE, LITHOGRAPHIC-FIELD, AND WAFER-SIZE TRENDS

Despite the continuous reduction in feature size of about 30% every three years, the size of first DRAM product demonstration in technical forums such as the IEEE International Solid State Circuits Conference (ISSCC) has continued to double every six years (an increase of about 12%/year). This increase in chip area has been necessary to accommodate 59% more bits/capacitors/transistors per year in accordance with Moore's Law (historically doubling functions per chip every 1.5–2 years). However, to maintain the historical trend of reducing cost/function by ~25–30%/year, it is necessary to continuously enhance equipment productivity, increase manufacturing yields, use the largest wafer size available, and, most of all, increase the number of chips available on a wafer.

The increase in the gross number of chips available on a wafer is primarily obtained by reducing the area of the chip by means of a combination of smaller feature size (shrink/scaling) and product/process redesign (compaction). For instance, using the latest models, it is forecast that the introduction chip area of a cost-effective product generation [which doubles the inter-generation (generation-to-generation) functionality every two years] must either remain as flat as possible. Furthermore, the area must be shrunk at an intra-generation (within a generation) annual reduction rate of 50% (the square of the .7× lithography reduction rate) during every technology node period.

In order for affordable DRAM products to achieve virtually flat intra-generation chip-sizes, they must also maintain a cell area array efficiency ratio of 63% of total chip area. Therefore, DRAM products require reduction of cell area design factors (cell area in units of minimum-feature-size-squared). The PIDS and FEP ITWGs have provided member survey data for the array efficiency targets, the cell area factors, and bits per chip. In addition, detailed challenges and needs for solutions to meet the aggressive cell area goals are documented in the Front End Processes chapter. Due to the importance of tracking/coordinating these new challenges, the DRAM cell area factor, the target cell sizes, and the cell array area percentage of total chip-size line items will continue to be tracked in ORTC Tables 1c, d, e, and f. (also refer to the Glossary for additional details). Notably, the reduction rate of DRAM cell area factors for the *2003 ITRS* models has been slowed significantly (the 6 factor moved from 2003 to 2008, and the 4 factor has been increased to 5 and moved from 2011 to 2016). In order to maintain the goal of flat chip sizes, the *2003 ITRS* DRAM chip size model now includes more aggressive array efficiency targets, and the rate of increase of "Moore's Law" bits per chip targets has been slowed from 2× every three years.

In the 2001 ITRS the Design ITWG improved the MPU chip size model to update with the latest transistor densities, large on-chip SRAM, and smaller target chip sizes. The Design ITWG has also added additional detail to the model, including transistor design improvement factors. The Design ITWG notes that design improvements occur at a slow rate in SRAM transistors and very little in logic gate transistors. Almost all the "shrink" and density improvement comes from lithography-enabled interconnect half-pitch scaling alone.

The present 2003 *ITRS* MPU chip size model is unchanged from the 2001 *ITRS*, and continues to reflect the additional competitive requirements for affordability and power management by targeting flat chip size trends for both high-performance MPUs (310 mm<sup>2</sup>) and cost-performance MPUs (140 mm<sup>2</sup>). Due to the MPU two-year-cycle half-pitch "catch-up phase" through the year 2004, the MPU products may be able to maintain flat chip sizes due to lithography improvements alone. However, after 2004, the inter-generation MPU chip size model, which is indexed to the ITRS technology node, can remain flat only by slowing the rate of on-chip transistors to double every technology node.

Due to the forecasted return to a three-year technology node cycle, the present MPU chip-size model slows the Moore's Law rate of on-chip transistors to 2× every three years. In order to maintain a flat chip size target and also return to the historical doubling every two years of on-chip functionality (transistors), MPU chip and process designers must add additional design/process improvements to the fundamental lithography-based scaling trends. The new target metrics of the MPU model are summarized in Tables 1g, h, i, and j.

To improve productivity, it is necessary to increase the output of good chips at each step in the fabrication process. The ability of printing multiple chips in a single exposure is a key productivity driver and is determined by the field size of the lithographic tool and the size and aspect ratio of the chips being printed on the wafer. In the past, lithography exposure field sizes doubled every other technology node to meet the demand for increasing chip sizes. The result was the achievement of very large step-and-scan fields  $(25\times32 = 800 \text{ mm}^2)$  by 1999. However, the Lithography ITWG indicates that maintaining the large field size under continued reduction of exposure features is increasing costs dramatically. Therefore, the ITWG forecasts of a requirement for the economically affordable lithography field was reduced to  $572 \text{ mm}^2$  (22×26) by the 90 nm node. After addition review, the Lithography TWG increased the "Affordable" field size to 704 mm<sup>2</sup> (22×32) for the 2003 *ITRS*. That trend is shown in Tables 2a and b.

DRAM chip sizes were deemed to be the most appropriate driver of affordable lithography field sizes. In the 2003 ITRS chip-size model for DRAMs, the introduction-level chip size is targeted to be smaller than the new affordable 704 mm<sup>2</sup> lithography field size, fitting at least one introduction-level chip size within the field. The new production-level DRAM chip size model (less than 140 mm<sup>2</sup> flat target) fits four die within the affordable field. The combination of technology-node scaling and cell design improvements (A-factor reduction) accomplishes that goal, while also maintaining a goal of doubling on-chip bits every two years. However, as mentioned above, the slowing of DRAM design improvements causes a requirement to add fewer on-chip bits to stay under the affordable lithography field limit. This accomplished in the present DRAM model by slowing the Moore's Law bits/chip rate to  $2\times/2.5$  to three years, as required. The data targets for the DRAM model are included in Tables 1c, d, e, and f.

Both the DRAM and MPU models depend upon achieving the aggressive DRAM and MPU design and process improvement targets. If those targets slip, then pressure will increase to print chip sizes larger than the present roadmap, or further slow the rate of "Moore's-Law" on-chip functionality. Either of these consequences will result in a negative impact upon cost-per-function reduction rates—the classical measure of our industries productivity-improvement and competitiveness.

With increasing cost reduction pressures, the need for the 300 mm productivity boost will also increase in urgency, especially for leading-edge manufacturers, but the poor economy has created financial challenges and limited capital investment. The maximum substrate diameter in Tables 2a and b (and in additional detail in the FEP chapter) is consistent with the ramp of 300 mm capacity beginning 2001. Also, the first manufacturing capability for the next  $1.5 \times$  wafer size conversion to 450 mm diameter is not anticipated to be required until 2011–2012 in the present roadmap. However, should the other productivity-improvement drivers (lithography and design/process improvements) fail to stay on schedule, there would be a need to accelerate the use of increased wafer diameter, or an equivalent processing platform, as a productivity improvement.

The effects of future technology acceleration/deceleration and the timing of the next wafer generation conversion requires the development and application of comprehensive long-range factory productivity and industry economic models. Such industry economic modeling (IEM) work is being sponsored and carried out jointly by Semiconductor Equipment and Materials International (SEMI) and International SEMATECH.

| Year of Production                             | 2003      | 2004       | 2005       | 2006        | 2007 | 2008 | 2009 |

|------------------------------------------------|-----------|------------|------------|-------------|------|------|------|

| Technology Node                                |           | hp90       |            |             | hp65 |      |      |

| DRAM ½ Pitch (nm)                              | 100       | 90         | 80         | 70          | 65   | 57   | 50   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)             | 120       | 107        | 95         | 85          | 76   | 67   | 60   |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)      | 107       | 90         | 80         | 70          | 65   | 57   | 50   |

| MPU Printed Gate Length (nm) ††                | 65        | 53         | 45         | 40          | 35   | 32   | 28   |

| MPU Physical Gate Length (nm)                  | 45        | 37         | 32         | 28          | 25   | 22   | 20   |

| Lithography Field Size                         |           |            |            |             |      |      |      |

| Lithography Field Size—area (mm <sup>2</sup> ) | 704       | 704        | 704        | 704         | 704  | 704  | 704  |

| Lithographic field size—length (mm)            | 32        | 32         | 32         | 32          | 32   | 32   | 32   |

| Lithographic field size—width (mm)             | 22        | 22         | 22         | 22          | 22   | 22   | 22   |

| Maximum Substrate Diameter (mm)—High-volu      | me Produc | tion (>20K | wafer star | ts per mont | h)   | -    | •    |

| Bulk or epitaxial or SOI wafer                 | 300       | 300        | 300        | 300         | 300  | 300  | 300  |

Table 2a Lithographic-Field and Wafer-Size Trends—Near-term Years

| 0 1                                                | 5 - 5              |             | 0     |      |      |      |

|----------------------------------------------------|--------------------|-------------|-------|------|------|------|

| Year of Production                                 | 2010               | 2012        | 2013  | 2015 | 2016 | 2018 |

| Technology Node                                    | hp45               |             | hp32  |      | hp22 |      |

| DRAM ½ Pitch (nm)                                  | 45                 | 35          | 32    | 25   | 22   | 18   |

| MPU/ASIC Metal 1 (M1) 1/2 Pitch (nm)               | 54                 | 42          | 38    | 30   | 27   | 21   |

| MPU/ASIC 1/2 Pitch (nm) (Un-contacted Poly)        | 45                 | 35          | 32    | 25   | 22   | 18   |

| MPU Printed Gate Length (nm) ††                    | 25                 | 20          | 18    | 14   | 13   | 10   |

| MPU Physical Gate Length (nm)                      | 18                 | 14          | 13    | 10   | 9    | 7    |

| Lithography Field Size                             | ·                  |             |       |      |      |      |

| Lithography Field Size—area (mm <sup>2</sup> )     | 704                | 704         | 704   | 704  | 704  | 704  |

| Lithographic field size—length (mm)                | 32                 | 32          | 32    | 32   | 32   | 32   |

| Lithographic field size—width (mm)                 | 22                 | 22          | 22    | 22   | 22   | 22   |

| Maximum Substrate Diameter (mm)—High-volume Produc | tion (>20K wafer s | tarts per m | onth) |      |      |      |

| Bulk or epitaxial or SOI wafer                     | 300                | 450         | 450   | 450  | 450  | 450  |

Table 2b Lithographic-Field and Wafer Size Trends—Long-term Years

## PERFORMANCE OF PACKAGED CHIPS

#### NUMBER OF PADS AND PINS / PAD PITCH, COST PER PIN, FREQUENCY

The demand for a higher number of functions on a single chip requires the integration of an increased number of transistors or bits (memory cells) for each product generation. Typically, the number of pads and pins necessary to allow Input/Output (I/O) signals to flow to and from an integrated circuit increases as the number of transistors on a chip increases. (Refer to Tables 3a and b)

Additional power and ground connections to the chip are also necessary to optimize power management and to increase noise immunity. Based upon chip pad-count numbers supplied by the Test ITWG, logic products (MPUs and high-performance ASICs) both approach 4–6K pads over the *ITRS* period. The MPU products are forecast to increase the total number of pads through this period by nearly 50%, and the ASICs double the maximum number of pads per chip. The two product types also differ significantly in the ratio of power/ground pads. The MPU product pad counts typically have 1:3 signal I/O pads and 2:3 power and ground pads, or two power/ground pads for every signal I/O pad. Unlike MPUs, high-performance ASIC product pad counts typically include one power/ground pad for each signal I/O pad.

| Year of Production                                                   | 2003         | 2004      | 2005      | 2006      | 2007      | 2008      | 2009      |

|----------------------------------------------------------------------|--------------|-----------|-----------|-----------|-----------|-----------|-----------|

| Technology Node                                                      |              | hp90      |           |           | hp65      |           |           |

| DRAM ½ Pitch (nm)                                                    | 100          | 90        | 80        | 70        | 65        | 57        | 50        |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                   | 120          | 107       | 95        | 85        | 76        | 67        | 60        |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)                            | 107          | 90        | 80        | 70        | 65        | 57        | 50        |

| MPU Printed Gate Length (nm) ††                                      | 65           | 53        | 45        | 40        | 35        | 32        | 28        |

| MPU Physical Gate Length (nm)                                        | 45           | 37        | 32        | 28        | 25        | 22        | 20        |

| Number of Chip I/Os (Number of Total C                               | hip Pads)—Ma | ximum     |           |           |           |           |           |

| Total pads—MPU                                                       | 3,072        | 3,072     | 3,072     | 3,072     | 3,072     | 3,328     | 3,584     |

| Signal I/O—MPU (1/3 of total pads)                                   | 1,024        | 1,024     | 1,024     | 1,024     | 1,024     | 1,109     | 1,195     |

| Power and ground pads—MPU (2/3 of total pads)                        | 2,048        | 2,048     | 2,048     | 2,048     | 2,048     | 2,219     | 2,389     |

| Total pads—ASIC high-performance                                     | 3,400        | 3,600     | 4,000     | 4,200     | 4,400     | 4,600     | 4,800     |

| Signal I/O pads—ASIC high-<br>performance                            | 1,700        | 1,800     | 2,000     | 2,100     | 2,200     | 2,300     | 2,400     |

| Power and ground pads—<br>ASIC high-performance (½ of total<br>pads) | 1,700        | 1,800     | 2,000     | 2,100     | 2,200     | 2,300     | 2,400     |

| Number of Total Package Pins-Maximu                                  | m [1]        |           |           |           |           |           |           |

| Microprocessor/controller,<br>cost-performance                       | 500–1,452    | 500–1,600 | 550–1,760 | 550–1,936 | 600–2,140 | 660–2,354 | 720–2,568 |

| Microprocessor/controller, high-<br>performance                      | 1,452        | 1,600     | 1,760     | 1,936     | 2,140     | 2,354     | 2,568     |

| ASIC (high-performance)                                              | 2,400        | 3,000     | 3,400     | 3,800     | 4,000     | 4,400     | 4,600     |

Table 3a

Performance of Packaged Chips: Number of Pads and Pins—Near-term Years

Notes for Tables 3a and 3b:

[1] Pin counts will be limited for some applications where fine pitch array interconnect is used by PWB technology and system cost.

The highest pin count applications will as a result use larger pitches and larger package sizes.

The reference to signal pin ratio will also vary greatly dependent on applications with an expected range from 2:1 to 1:4.

Table 3b Performance of Packaged Chips: Number of Pads and Pins-Long-term Years

| Year of Production                                            | 2010          | 2012          | 2013           | 2015           | 2016           | 2018           |

|---------------------------------------------------------------|---------------|---------------|----------------|----------------|----------------|----------------|

| Technology Node                                               | hp45          |               | hp32           |                | hp22           |                |

| DRAM ½ Pitch (nm)                                             | 45            | 35            | 32             | 25             | 22             | 18             |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                            | 54            | 42            | 38             | 30             | 27             | 21             |

| MPU/ASIC 1/2 Pitch (nm) (Un-contacted Poly)                   | 45            | 35            | 32             | 25             | 22             | 18             |

| MPU Printed Gate Length (nm) ††                               | 25            | 20            | 18             | 14             | 13             | 10             |

| MPU Physical Gate Length (nm)                                 | 18            | 14            | 13             | 10             | 9              | 7              |

| Number of Chip I/Os (Number of Total Chip Pads)—Maximum       |               |               |                |                |                |                |

| Total pads—MPU                                                | 3,840         | 4,096         | 4,224          | 4,352          | 4,416          | 4,544          |

| Signal I/O—MPU (1/3 of total pads)                            | 1,280         | 1,365         | 1,408          | 1,451          | 1,472          | 1,515          |

| Power and ground pads—MPU (2/3 of total pads)                 | 2,560         | 2,731         | 2,816          | 2,901          | 2,944          | 3,029          |

| Total pads—ASIC high-performance                              | 4,800         | 5,200         | 5,400          | 5,800          | 6,000          | 6,400          |

| Signal I/O pads—ASIC high-performance                         | 2,400         | 2,600         | 2,700          | 2,900          | 3,000          | 3,200          |

| Power and ground pads—ASIC high-performance (½ of total pads) | 2,400         | 2,600         | 2,700          | 2,900          | 3,000          | 3,200          |

| Number of Total Package Pins—Maximum [1]                      |               |               |                |                |                |                |

| Microprocessor/controller, cost-performance                   | 780–<br>2,782 | 936–<br>3,338 | 1014–<br>3,616 | 1217–<br>4,340 | 1318–<br>4,702 | 1521–<br>5,426 |

| Microprocessor/controller, high-performance                   | 2,782         | 3,338         | 3,616          | 4,340          | 4,702          | 5,426          |

| ASIC (high-performance)                                       | 4,009         | 4,810         | 5,335          | 6,402          | 7,042          | 8,450          |

Package pin count (Tables 3a and 3b) and cost-per-pin (Tables 4a and 4b), provided by the Assembly and Packaging ITWG, point out challenges to future manufacturing economics. Based upon the projected growth in the number of transistors/chip, it is forecast that the number of package pin/balls will continue to grow at an annual rate of approximately 10%, while the cost/pin decreases at 5%/year. These trends make it more challenging for suppliers of packaging technologies to deliver cost-effective solutions, because the overall average cost of packaging will increase annually at 5%/year (.95 cost/pin × 1.10 pins/year = 1.05 cost/year).

In the very competitive consumer electronics product environment, prices for high-volume, high-tech products such as PCs and cell phones tend to remain flat or even decrease. These same high-tech products typically also deliver twice the performance every two years. This is the end-use market environment of the leading-edge semiconductor manufacturer, and it is the fundamental economic driver behind the *ITRS* economic requirement to reduce cost per function (bits, transistors) at an annual 30% or faster rate ( $2 \times$  functionality/chip at flat price every two years = 29%/year).

If future semiconductor component products must be targeted to maintain constant or decreasing prices and the average number of pins per unit increases at 10% while the average cost per pin decreases at only 5%, then the following will occur:

- 1. the average packaging share of total product cost will double over the 15-year roadmap period, and

- 2. the ultimate result will be greatly reduced gross profit margins and limited ability to invest in R&D and factory capacity.

This conclusion is one of the drivers behind the industry trends to reduce the overall system pin requirements by combining functionality into Systems-on-Chip (SoC) and through the use of multi-chip modules, bumped chip-on-board (COB), and other creative solutions.

In addition to the need to increase functionality while exponentially decreasing cost per function, there is also a market demand for higher-performance, cost-effective products. Just as Moore's Law predicts that functions-per-chip will double every 1.5–2 years to keep up with consumer demand, there is a corresponding demand for processing electrical signals at progressively higher rates. In the case of MPUs, processor instructions/second have also historically doubled every 1.5–2 years. For MPU products, increased processing power, measured in millions of instructions per second (MIPs), is accomplished through a combination of "raw technology performance" (clock frequency) multiplied by "architectural performance" (instructions per clock cycle). The need for a progressively higher operational frequency will continue to demand the development of novel process, design, and packaging techniques.

These considerations are reflected in Tables 4c and 4d, which includes line items contributed by the Design ITWG and the Assembly and Packaging ITWG to forecast the maximum on-chip and chip-to-board frequency trends. The highest frequency obtainable in each product generation is directly related to the intrinsic transistor performance (on-chip, local clock). The difference between this "local" frequency and the frequency of signals traveling across the chip increases due to degradation of signal propagation delay caused by line-to-line and line-to-substrate capacitive coupling. Additional signal degradation is associated with the inductance of wire bonds and package leads. Direct chip attachment may eventually be the only viable way to eliminate any parasitic effect introduced by the package. To optimize signal and power distribution across the chip, it is expected that the number of layers of interconnect will continue to increase. As size downscaling of interconnect also continues, wider use of copper (low resistivity) and various inter-metal insulating materials of progressively lower dielectric constant ( $\kappa$ -2–3) will be adopted in the chip fabrication process. Multiplexing techniques will also be used to increase the chip-to-board operating frequency (off-chip).

| Year of Production                                                     | 2003      | 2004     | 2005     | 2006     | 2007     | 2008     | 2009    |

|------------------------------------------------------------------------|-----------|----------|----------|----------|----------|----------|---------|

| Technology Node                                                        |           | hp90     |          |          | hp65     |          |         |

| DRAM 1/2 Pitch (nm)                                                    | 100       | 90       | 80       | 70       | 65       | 57       | 50      |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                     | 120       | 107      | 95       | 85       | 76       | 67       | 60      |

| MPU/ASIC ½ Pitch (nm)<br>(Un-contacted Poly)                           | 107       | 90       | 80       | 70       | 65       | 57       | 50      |

| MPU Printed Gate Length (nm) ††                                        | 65        | 53       | 45       | 40       | 35       | 32       | 28      |

| MPU Physical Gate Length (nm)                                          | 45        | 37       | 32       | 28       | 25       | 22       | 20      |

| Chip Pad Pitch (micron)                                                |           |          |          |          |          |          |         |

| Pad pitch—ball bond                                                    | 40        | 35       | 30       | 25       | 25       | 20       | 20      |

| Pad pitch—wedge bond                                                   | 30        | 25       | 20       | 20       | 20       | 20       | 20      |

| Pad pitch—wedge bond                                                   | 30        | 25       | 20       | 20       | 20       | 20       | 20      |

| Pad Pitch—area array flip-chip<br>(cost-performance, high-performance) | 150       | 150      | 130      | 130      | 120      | 110      | 100     |

| Pad Pitch—peripheral flip-chip<br>(handheld, low-cost, harsh)          | 60        | 60       | 40       | 40       | 30       | 30       | 20      |

| Cost-Per-Pin                                                           |           |          |          |          |          |          |         |

| Package cost (cents/pin)<br>(cost-performance)—<br>minimum-maximum     | .75–1.30  | .71–1.24 | .67–1.17 | .64–1.11 | .61–1.05 | .58–1.00 | .55–.96 |

| Package cost (cents/pin) (Memory)—<br>minimum–maximum                  | 0.30-0.56 | 0.29–.53 | .27–.50  | ,26–.48  | ,25–.45  | .23–.43  | .22–.41 |

Table 4a Performance and Package Chips: Pads, Cost—Near-term Years

Table 4b

Performance and Package Chips: Pads, Cost—Long-term Years

| Year of Production                                                      | 2010      | 2012      | 2013      | 2015      | 2016      | 2018      |

|-------------------------------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|

| Technology Node                                                         | hp45      |           | hp32      |           | hp22      |           |

| DRAM ½ Pitch (nm)                                                       | 45        | 35        | 32        | 25        | 22        | 18        |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                      | 54        | 42        | 38        | 30        | 27        | 21        |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)                               | 45        | 35        | 32        | 25        | 22        | 18        |

| MPU Printed Gate Length (nm) ††                                         | 25        | 20        | 18        | 14        | 13        | 10        |

| MPU Physical Gate Length (nm)                                           | 18        | 14        | 13        | 10        | 9         | 7         |

| Chip Pad Pitch (micron)                                                 |           |           |           |           |           |           |

| Pad pitch—ball bond                                                     | 20        | 20        | 20        | 20        | 20        | 20        |

| Pad Pitch—wedge bond                                                    | 20        | 20        | 20        | 20        | 20        | 20        |

| Pad Pitch—area array flip-chip (cost-performance, high-<br>performance) | 100       | 90        | 90        | 80        | 80        | 70        |

| Pad Pitch-peripheral flip-chip (handheld, low-cost, harsh)              | 20        | 20        | 20        | 15        | 15        | 15        |

| Cost-Per-Pin                                                            | •         | •         | •         | •         | •         | •         |

| Package cost (cents/pin) (cost-performance)— minimum-maximum            | 0.52-0.94 | 0.5–.86   | 0.5–.77   | 0.5-0.69  | 0.5-0.65  | 0.5-0.59  |

| Package cost (cents/pin) (Memory)— minimum-maximum                      | .22–.41   | 0.22-0.36 | 0.22-0.35 | 0.22-0.31 | 0.22-0.29 | 0.22-0.27 |

| Year of Production                                                            | 2003  | 2004  | 2005  | 2006  | 2007  | 2008   | 2009   |

|-------------------------------------------------------------------------------|-------|-------|-------|-------|-------|--------|--------|

| Technology Node                                                               |       | hp90  |       |       | hp65  |        |        |

| DRAM ½ Pitch (nm)                                                             | 100   | 90    | 80    | 70    | 65    | 57     | 50     |

| MPU/ASIC Metal 1 (M1) <sup>1</sup> / <sub>2</sub> Pitch (nm)                  | 120   | 107   | 95    | 85    | 76    | 67     | 60     |

| MPU/ASIC 1/2 Pitch (nm) (Un-contacted Poly)                                   | 107   | 90    | 80    | 70    | 65    | 57     | 50     |

| MPU Printed Gate Length (nm) ††                                               | 65    | 53    | 45    | 40    | 35    | 32     | 28     |

| MPU Physical Gate Length (nm)                                                 | 45    | 37    | 32    | 28    | 25    | 22     | 20     |

| Chip Frequency (MHz)                                                          |       | •     |       | •     | •     | •      |        |

| On-chip local clock                                                           | 2,976 | 4,171 | 5,204 | 6,783 | 9,285 | 10,972 | 12,369 |

| Chip-to-board (off-chip) speed<br>(high-performance, for peripheral buses)[1] | 2,000 | 2,500 | 3,125 | 3,906 | 4,883 | 6,103  | 7,629  |

| Maximum number wiring levels—maximum                                          | 13    | 14    | 15    | 15    | 15    | 16     | 16     |

| Maximum number wiring levels—minimum                                          | 9     | 10    | 11    | 11    | 11    | 12     | 12     |

Table 4c Performance and Package Chips: Frequency On-chip Wiring Levels—Near-term Years

Table 4d Performance and Package Chips: Frequency, On-chip Wiring Levels—Long-term Years

| Year of Production                                                            | 2010   | 2012   | 2013   | 2015   | 2016   | 2018   |

|-------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|

| Technology Node                                                               | hp45   |        | hp32   |        | hp22   |        |

| DRAM <sup>1</sup> / <sub>2</sub> Pitch (nm)                                   | 45     | 35     | 32     | 25     | 22     | 18     |